طراحی و شبیه سازی یک تقویت کننده ترارسانایی خط تا خط ولتاژ کم و بهره بالا

- سال انتشار: 1396

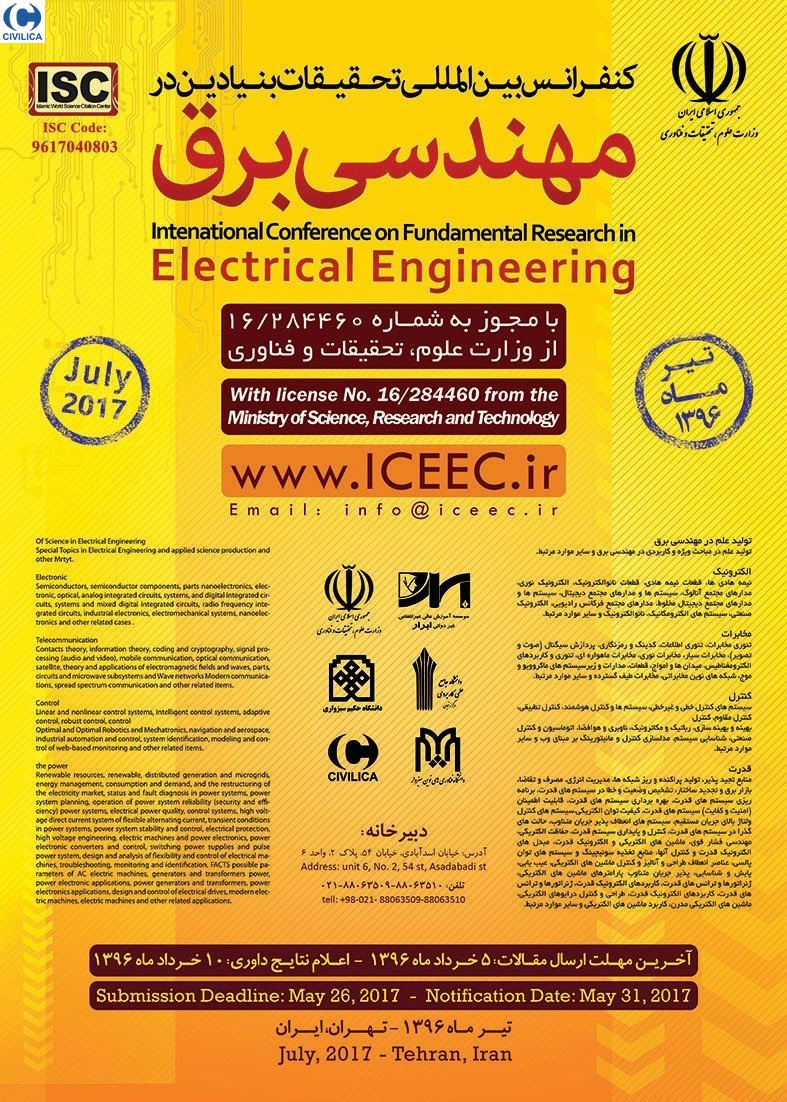

- محل انتشار: کنفرانس بین المللی تحقیقات بنیادین در مهندسی برق

- کد COI اختصاصی: ICEEC01_198

- زبان مقاله: فارسی

- تعداد مشاهده: 453

نویسندگان

گروه برق، دانشکده فنی و مهندسی، دانشگاه بناب، بناب، ایران

استادیار گروه برق، دانشکده فنی و مهندسی، دانشگاه بناب، بناب، ایران

چکیده

در این مقاله، یک مدار تقویت کننده ترارسانایی عملیاتی دو طبقه در تکنولوژی 180 نانومتر CMOS برای کاربردهای ولتاژ پایین ارایه شده است. در طراحی این مدار از یک طبقه ورودی تقویت کننده خط تا خط که مبتنی بر روش نوینی برای ثابت نگه داشتن gm است و باعث بهبود سویینگ خروجی می شود، و طبقه خروجی پوش پول که باعث بهبود آهنگ گردش می شود، استفاده شده است. تقویت کننده ترارسانایی دو طبقه طراحی شده، دارای پهنای باند بهره واحد 7/1 مگاهرتز می باشد که به ازای بهره 62 دسی بل دریافت می شود. ولتاژ منبع تغذیه آن 1/5 ولت است و توان مصرفی در این مدار در حدود 351 میکرووات می باشد که در مقایسه با کارهای مشابه کاهش یافته است. CMRR برای این مدار 79/5 دسی بل، همچنین حاشیه فاز در حدود 51 درجه است که باعث می شود مدار پایداری خوبی داشته باشد.کلیدواژه ها

تقویت کننده ترارسانایی، خط تا خط، ولتاژ کم، بهره بالا، تکنیک ثابت نگه داشتن gmمقالات مرتبط جدید

- کاشت یون در نیمه رساناها: تاریخچه، فرایند، اثرات، کاربردها، چالش ها

- تخمین نفوذ مس در نوارهای لبه ای با استفاده از شبکه های عصبی عمیق

- آینده ی تولید غذا با اینترنت اشیاء

- پیشرفتهای نوین در یکپارچه سازی فرآیند دوقطبی در فناوری های میکروالکترونیک

- آخرین پیشرفتها در فناوری کاشت یون در سیلیکون کاربید و گالیوم نیترید

اطلاعات بیشتر در مورد COI

COI مخفف عبارت CIVILICA Object Identifier به معنی شناسه سیویلیکا برای اسناد است. COI کدی است که مطابق محل انتشار، به مقالات کنفرانسها و ژورنالهای داخل کشور به هنگام نمایه سازی بر روی پایگاه استنادی سیویلیکا اختصاص می یابد.

کد COI به مفهوم کد ملی اسناد نمایه شده در سیویلیکا است و کدی یکتا و ثابت است و به همین دلیل همواره قابلیت استناد و پیگیری دارد.